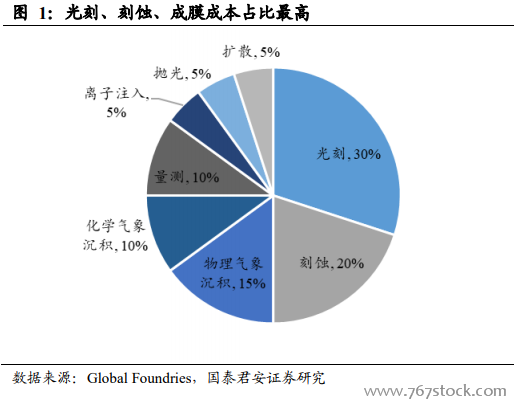

晶圓制造是半導體生產的必要環節,它是指利用二氧化硅作為原材料制作單晶硅硅片的過程。具體來講,是先利用西門子工藝,將天然硅加工成用來制作芯片的高純硅,后者又被稱為半導體級硅或電子級硅,再利用 CZ 法等技術將半導體級硅的多晶硅塊轉換成一塊大的單晶硅硅錠。對硅錠進行一系列機械加工、化學處理、表面拋光和質量測量后,可以得到用于下一步晶圓加工的硅片。

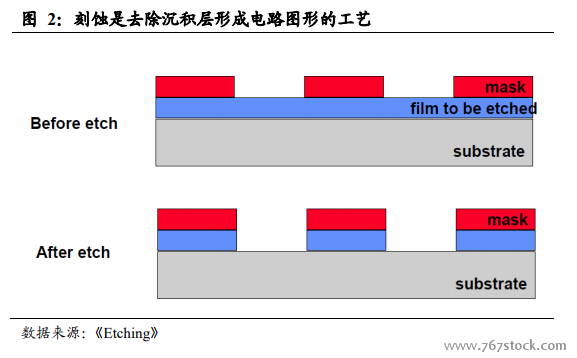

刻蝕是用化學或物理方法對襯底表面或表面覆蓋薄膜進行選擇性腐蝕或剝離的過程,進而形成光刻定義的電路圖形。刻蝕的基本目標是在涂膠的硅片上正確的復制掩模圖形。有圖形的光刻膠層在刻蝕中不受到腐蝕源顯著的侵蝕。這層掩蔽膜用來在刻蝕中保護硅片上的特殊區域而選擇性地刻蝕掉未被光刻膠保護的區域。在通常的 CMOS 工藝流程中,刻蝕都是在光刻工藝之后進行的。從這一點來看,刻蝕可以看成在硅片上復制所想要圖形的最后主要圖形轉移工藝步驟。

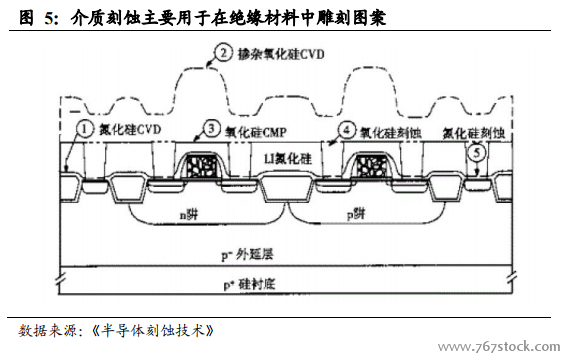

介質刻蝕在絕緣材料中雕刻圖案以將半導體器件的導電部分分隔開。 對于先進的設備,這些結構可能具有較高的深寬比,并且涉及復雜、敏感的材料。 與刻蝕參數目標輕微的偏差(即使在原子尺度)也會對器件的質量產生負面影響。介質刻蝕一般要求刻蝕出比較高深寬比的缺口,并且要求下層材料有較高的選擇比。

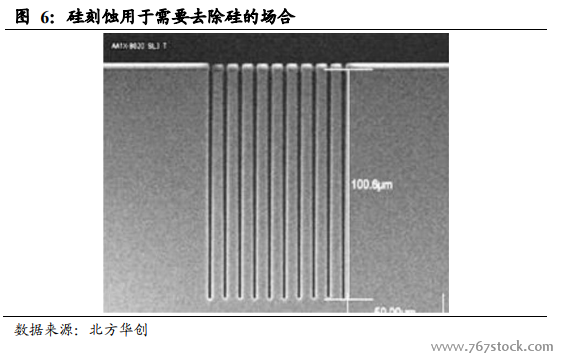

硅刻蝕用于需要去除硅的場合,淺溝槽隔離刻蝕(STI)、多晶硅柵極刻蝕(poly gate)是定義半導體器件尺寸的關鍵工序。由于技術的不斷推進,在傳統硅刻蝕的基礎上發展出了深硅刻蝕,它有別于 VLSI中的硅刻蝕,因此又稱為先進硅刻蝕(ASE) 工藝。它由于采用了感應耦合等離子體(ICP),所以與傳統的反應離子刻蝕(RIE)、電子回旋共振(ECR)等刻蝕技術相比,具有更大的各向異性刻蝕速率比和更高的刻蝕速率,且系統結構簡單。

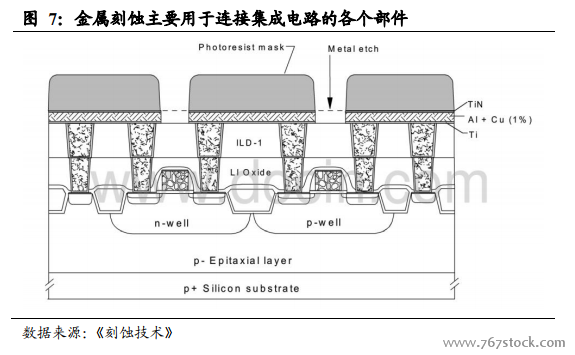

金屬蝕刻工藝在連接形成集成電路(IC)的各個部件(例如,形成電線和電連接)中起關鍵作用。 這些工藝還用于鉆穿金屬硬掩模(MHM),金屬硬掩模用于對傳統掩模太小的特征進行圖案化,從而允許特征尺寸的持續縮小。金屬刻蝕主要步驟分為去除氧化層(自然氧化的鋁)、刻蝕其他材料層(如抗反射層)、主刻蝕(鋁)、去除殘留物的過刻蝕、去除光刻膠。