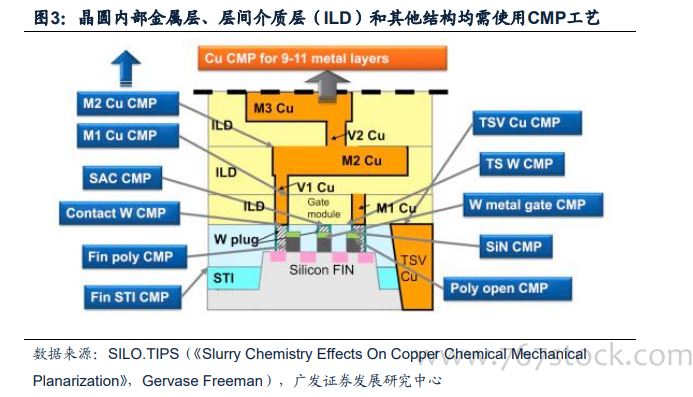

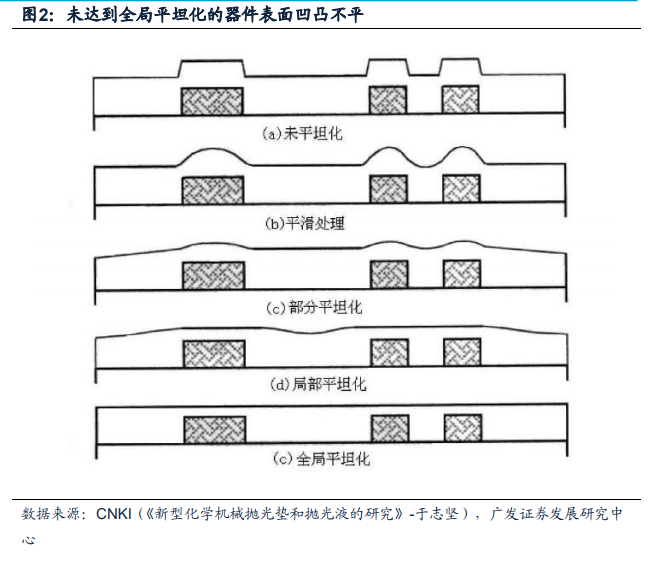

CMP是芯片制造關鍵技術,芯片制程的先進化推動拋光次數成倍增長。根據不同工藝制程和技術節點的要求,每一片晶圓在生產過程中都會經歷幾道甚至幾十道的拋光工藝步驟,CMP拋光工藝主要用于硅片及硅片以上金屬層、層間介質層(ILD)和其他結構的表面平坦化。

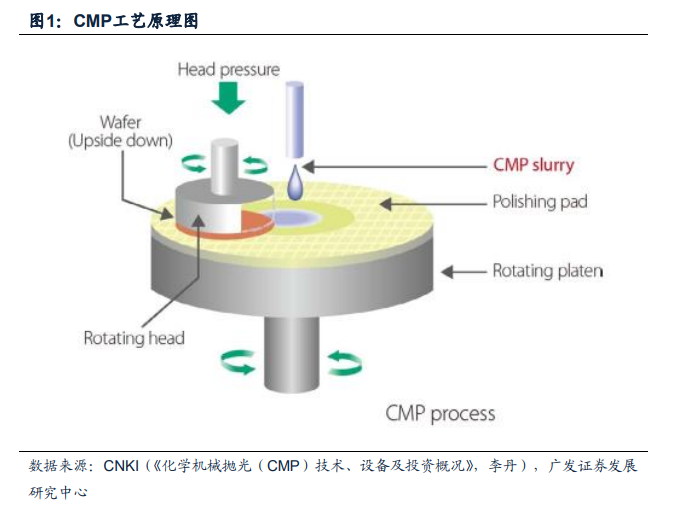

晶圓硅片平坦化:在集成電路生產中,最小特征尺寸小于0.35μm芯片的硅片表面必須進行全局平坦化,否則會對刻蝕的精確度和效率產生影響,導致接觸不良,漏電,電子轉移等問題。CMP是目前唯一能實現全局平坦化的技術(其他技術只能做到局部平坦化)。

金屬層、層間介質層(ILD)及其他結構平坦化:芯片工藝的先進化帶來金屬層、介質層等結構數量的增加,進而帶來拋光次數的增加。130nm制程芯片只有六層金屬層,而5nm制程芯片至少有14層金屬層,每層金屬之間沉積有一層層間介質層(ILD),隔離上下兩層金屬,最底部層間介質層(IDL)以下還可能存在鎢塞、淺槽隔離層(STI)、硅通孔(TSV)等結構。這些金屬層、層間介質層和其他結構表面都需CMP處理。根據杜邦數據,7nm以下邏輯芯片中,CMP拋光步驟約三十步,最先進芯片可達四十二步。