半導體制程工藝的發展,離不開摩爾定律。摩爾定律指出,當價格不變時,集成電路上可容納的元器件的數目,約每隔 18~24 個月便會增加一倍,性能也將提升一倍。隨著晶體管尺寸的減少,相同單位面積中可以容納更多的晶體管,相同大小的處理器可以獲得更高的處理能力。且小的晶體管消耗的功率少,這減少了芯片的總功耗,產生的熱量也隨之降低,因此可以進一步提高時鐘速度。

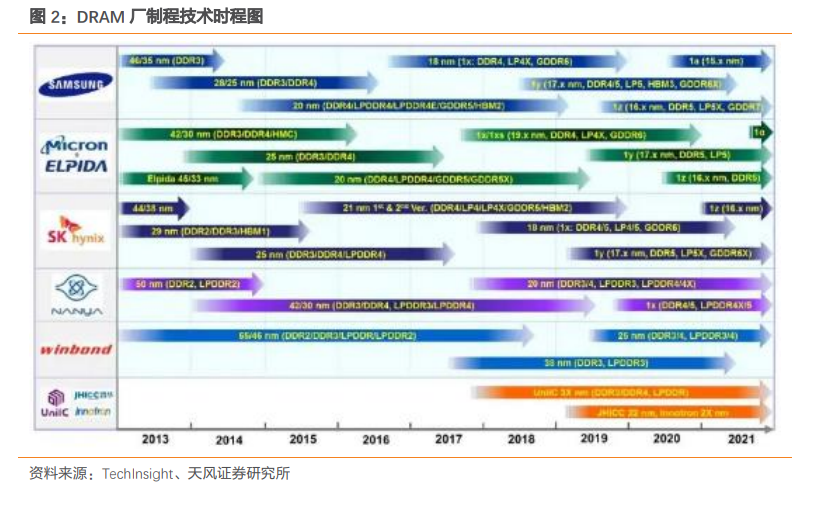

存儲芯片制程發展與邏輯芯片制程發展速度不太一致,但都受到摩爾定律的限制。DRAM目前最先進工藝位于 18-15nm 之間,通常認為 10nm 是物理極限。從 2016 年開始,供應商開始采用 1xnm 節點制,其中供應商在路線圖上擁有三種 DRAM 產品(1xnm,1ynm和 1znm)。最初,將 1xnm 節點定義為具有 17nm 至 19nm 幾何形狀的 DRAM,1ynm 是14nm 至 16nm,1znm 是 11nm 至 13nm。目前供應廠商的節點停留在 1xnm 狀態(1xnm,1ynm,1znm,新三代制程包括 1anm,1bnm,1cnm 都屬于 1xnm 節點機制)。各大廠商正在積極尋找新的解決方案,繼續擴展 DRAM 并提高性能,在未來的制程節點上可能會使用 EUV 光刻實現轉變。SK Hynix 計劃在 1anm 使用 EUV,該技術將于 2021 年面世。三星在 1znm 完成了對 DRAM 的 EUV 測試,但不會用于量產,可能會用于 1a 或 1b 的產品中。美光則計劃將 193nm 浸沒式光刻和 SADP 擴展到 1bnm。

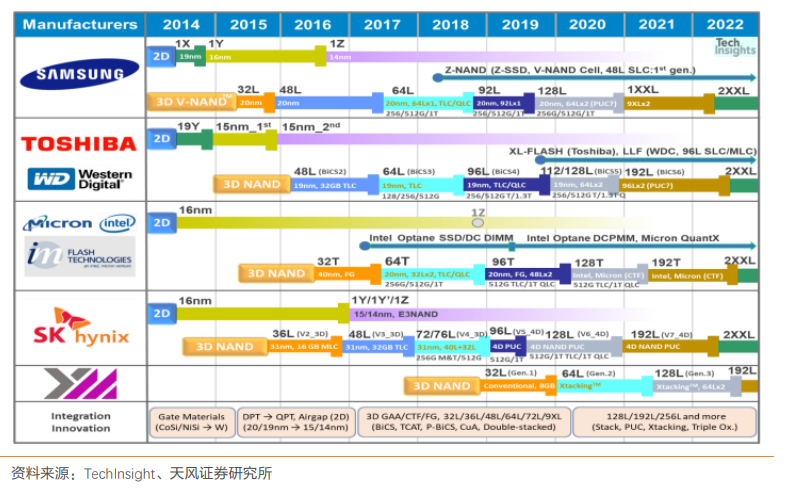

NAND 閃存驅動器的容量取決于芯片中的單元數量。在 2D NAND 結構中,存儲單元在單個管芯層中彼此相鄰放置,以提高存儲容量。單元尺寸從 120 nm 減小到 1x nm,使容量增加了 100 倍,且當前 15nm/14nm 已經達到了極限。2D NAND 技術存在兩個局限,一是單元縮小是依靠光刻技術實現的,當光刻技術到達極限時,單元無法進一步縮小;二是當存儲單元降至 20 nm 以下時,電荷從一個單元泄漏到另一個單元的機會大大增加,這種單元間干擾會導致數據損壞,從而嚴重損害閃存的可靠性。因此廠商們轉向 3D NAND,單元以垂直堆疊的方式來增加密度。3D 堆疊有單層堆棧和線堆棧兩種。在最新的 128 層中,廠商大多使用兩個 64 層進行堆疊,三星計劃單層堆疊,在沒有其他新突破的情況下,128 層是單層堆疊的極限。而線堆疊在 500 層也可能存在問題,因此還需要探索新的堆疊方法。